## Lecture 7: Logic design

- Binary digital logic circuits:

- Two voltage levels (ground and supply voltage) for 0 and 1

- Built from transistors used as on/off switches

- Analog circuits not very suitable for generic computing

- Digital logic with more than two states is not practical

Combinational logic: output depends only on the current inputs (no memory of past inputs)

Sequential logic: output depends on the current inputs as well as (some) previous inputs

### Combinational logic circuits

Inverter (or NOT gate): 1 input and 1 output "invert the input signal"

input \_\_\_\_\_ output

$$\begin{array}{c|c} IN & OUT \\ \hline 0 & 1 \\ 1 & 0 \end{array}$$

OUT = IN

AND gate: minimum 2 inputs and 1 output "output 1 only if both inputs are 1"

### Combinational logic circuits

• OR gate:

- "output 1 if at least one input is 1"

|            | IN <sub>1</sub> | $IN_2$ | OUT |                     |

|------------|-----------------|--------|-----|---------------------|

| $IN_1$     | 0               | 0      | 0   | OUT = INI + INI     |

| $IN_1$ OUT | 0               | 1      | 1   | $OUT = IN_1 + IN_2$ |

|            | 1               | 0      | 1   |                     |

|            | 1               | 1      | 1   |                     |

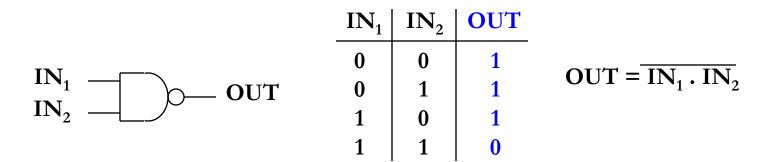

• NAND gate:

- "output 1 if both inputs are not 1" (NOT AND)

Inf2C Computer Systems - 2010-2011

### Combinational logic circuits

• NOR gate:

| "output 1 if no input is 1" (NOT OR) |                 |        |     |                                |  |  |  |

|--------------------------------------|-----------------|--------|-----|--------------------------------|--|--|--|

|                                      | IN <sub>1</sub> | $IN_2$ | ÓUT |                                |  |  |  |

| $IN_1$ OOUT                          | 0               | 0      | 1   | $OUT = \overline{IN_1 + IN_2}$ |  |  |  |

|                                      | 0               | 1      | 0   |                                |  |  |  |

|                                      | 1               | 0      | 0   |                                |  |  |  |

|                                      | 1               | 1      | 0   |                                |  |  |  |

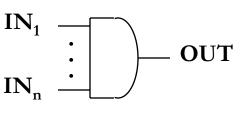

Multiple-input gates:

OUT = 1 if <u>all</u>  $IN_i = 1$

OUT = 1 if <u>any</u>  $IN_i = 1$

Inf2C Computer Systems - 2010-2011

### Multiplexer

Multiplexer: a circuit for selecting one of many inputs

$$i_{0} \xrightarrow{i_{0}} z \qquad z = \begin{cases} i_{0}, \text{ if } c=0\\ i_{1}, \text{ if } c=1 \end{cases}$$

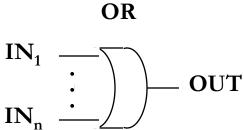

# A multiplexer implementation

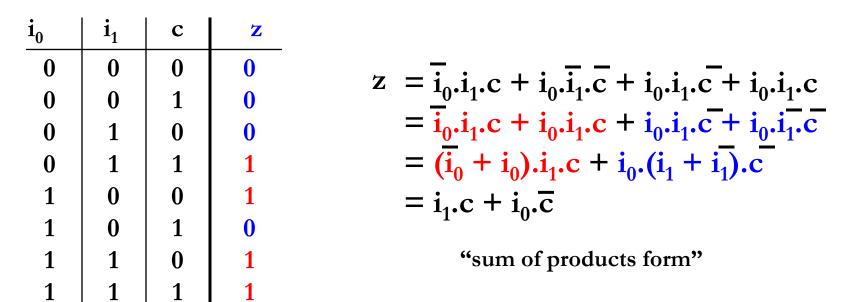

- Sum of products form:  $i_1 \cdot c + i_0 \cdot \overline{c}$

- Can be implemented with 1 inverter, 2 AND gates and 1 OR gate:  $i_1 \overline{)}$

- Sum of products is not practical for circuits with large number of inputs (n)

- The number of possible products can be proportional to  $2^n$

#### Arithmetic circuits

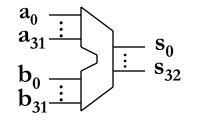

32-bit adder

64 inputs  $\rightarrow$  too complex for sum of products

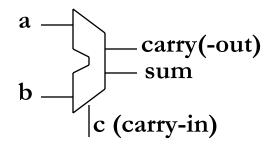

| dder: |

|-------|

|       |

sum =

$$\overline{a}.\overline{b}.c + \overline{a}.\overline{b}.\overline{c} + a.\overline{b}.\overline{c} + a.b.c$$

carry =  $b.c + a.c + a.b$

|   | a | b | c | carry | sum |

|---|---|---|---|-------|-----|

| - | 0 | 0 | 0 | 0     | 0   |

|   | 0 | 0 | 1 | 0     | 1   |

|   | 0 | 1 | 0 | 0     | 1   |

|   | 0 | 1 | 1 | 1     | 0   |

|   | 1 | 0 | 0 | 0     | 1   |

|   | 1 | 0 | 1 | 1     | 0   |

|   | 1 | 1 | 0 | 1     | 0   |

|   | 1 | 1 | 1 | 1     | 1   |

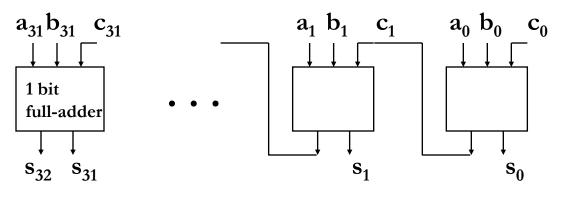

Ripple carry adder

32-bit adder: chain of 32 full adders

- Carry bits  $c_i$  are computed in sequence  $c_1, c_2, ..., c_{32}$ (where  $c_{32} = s_{32}$ ), as  $c_i$  depends on  $c_{i-1}$

- Since sum bits s<sub>i</sub> also depend on c<sub>i</sub>, they too are computed in sequence

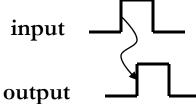

## Propagation Delays

- Propagation delay = time delay between input signal change and output signal change at the other end

- Delay depends on technology (transistor, wire capacitance, etc.) and number of gates driven by the gate's output (fan out)

- e.g.: Sum of products circuits: 3 2-input gate delays (inverter, AND, OR) → very fast!

- e.g.: 32-bit ripple carry adder: 65 2-input gate delays (1 AND + 1 OR for each of 31 carries to propagate; 1 inverter + 1 AND + 1 OR for S<sub>31</sub>) → slow

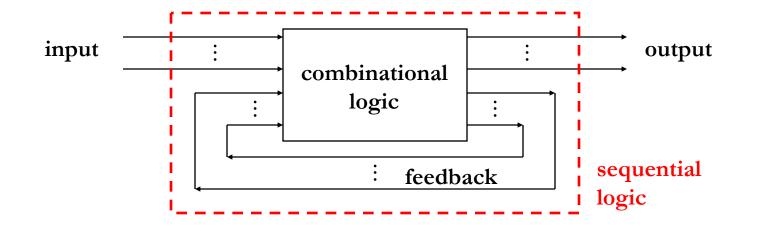

# Sequential logic circuits

- Output depends on current inputs as well as past inputs

- The circuit has memory

- Sequences of inputs generate sequences of

outputs  $\Rightarrow$  sequential logic

### Sequential logic circuits

- For a fixed input and *n* feedback signals, the circuit can have 2<sup>n</sup> possible different behaviours (states)

- E.g.  $n=1 \rightarrow$  one state if feedback signal = 0

one state if feedback signal = 1

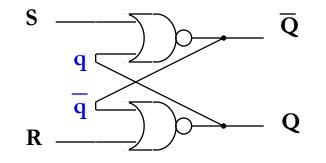

- Example: SR latch

- Inputs: R, S

- Feedback: q

- Output: Q

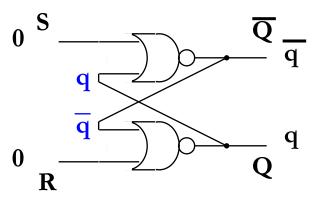

#### SR Latch

Truth table: S R  $\mathbf{Q}_{i}$  $\mathbf{Q}_{i-1}$ 0 0 1 0 0 0 u=unused 1 1 1 1 u

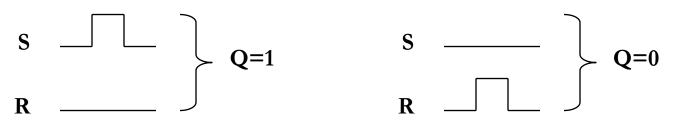

- Usage: 1-bit memory

- Keep the value in memory by maintaining S=0 and R=0

- Set the value in memory to 0 (or 1) by setting R=1 (or S=1) for a short time

Inf2C Computer Systems - 2010-2011

## Timing of events

- Asynchronous sequential logic

- State (and possibly output) of circuit changes whenever inputs change

- Synchronous sequential logic

- State (and possibly output) can only change at times synchronized to an external signal → the clock

Inf2C Computer Systems - 2010-2011

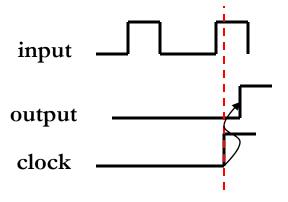

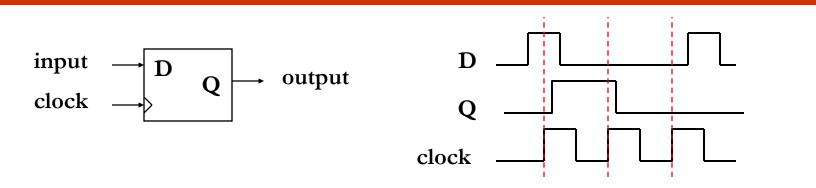

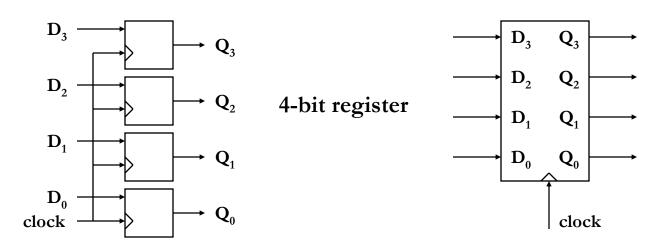

## D flip-flop

- Edge-triggered flip-flop: on a +ve clock edge, D is copied to Q

- Can be used to build registers:

Inf2C Computer Systems - 2010-2011

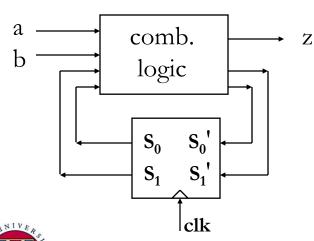

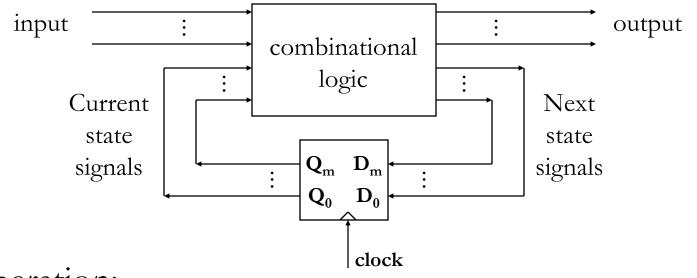

## General sequential logic circuit

Operation:

- At every rising clock edge next state signals are propagated to current state signals

- Current state signals plus inputs work through combinational logic and generate output and next state signals

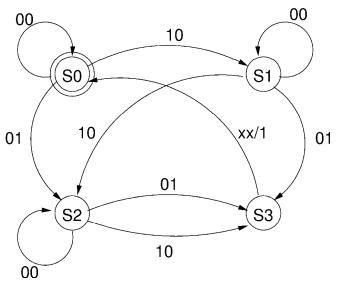

### Hardware FSM

- A sequential circuit is a (deterministic) Finite State Machine – FSM

- Example: Vending machine

- Accepts 10p, 20p coins, sells one product costing 30p, no change given

- Coin reader has 2 outputs: a,b for 10p, 20p coins respectively

- Output z asserted when 30p

or more has been paid in

Inf2C Computer Systems - 2010-2011

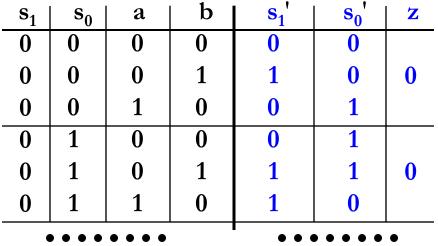

## FSM implementation

- Methodology:

- Choose encoding for states, e.g S0=00, ..., S3=11

- Build truth table for the next state  $s_1'$ ,  $s_0'$  and output z

- Generate logic equations for  $s_1'$ ,  $s_0'$ , z

- Design comb logic from logic equations and add stateholding register