# Handling Hazards

- Structural hazards

- Stalling: pipeline interlock

- Code scheduling

- Data hazards

- Stalling: pipeline interlock

- Forwarding

- Load delay

- Stalling: pipeline interlock

- Code scheduling: fill the load delay slot

- Control Hazards

- Early branch resolution

- Stalling: flushing the pipeline

- Delayed branch

- Predict non taken (or taken)

- Static branch prediction

- Dynamic branch prediction

- Recoverable exceptions is a challenge (e.g. pagefault, arithmetic exception)

- Instructions before must commit

- Instruction after must be killed

- Instructions causing exception must be re-executed with same operands

- Exceptions may overlap in pipeline, or even occur outof-order

- Handling of exception delayed until Instruction reaches last stage.

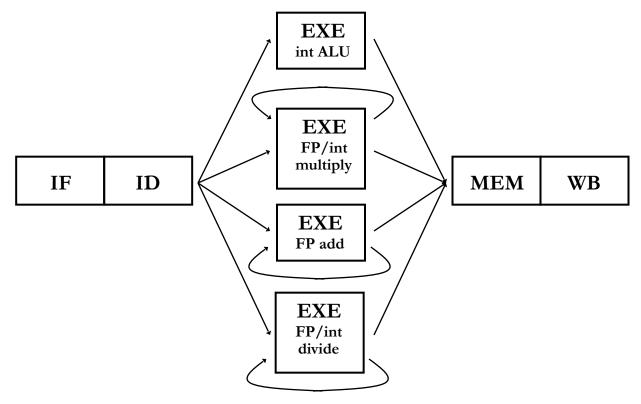

# **Multicycle Operations**

- Floating point operations take multiple cycles in EXE

- Assume a system with 1 int ALU, 1 FP/int multiplier, 1 FP adder, 1 FP/int divider

- Instruction latency: cycles to wait for the result of an instruction

- Usually the number of cycles for the execution pipeline minus 1

- e.g. 0 cycles for integer ALU since no wait is necessary

- Instruction initiation interval: time to wait to issue another instruction of the same type

- Not equal to number of cycles, if multicycle operation is pipelined or partially pipelined

- Examples:

- Integer ALU:

- 1 EXE cycle  $\rightarrow$  latency = 0; initiation interval = 1

- FP add, fully pipelined:

- 4 EXE cycles  $\rightarrow$  latency = 3; initiation interval = 1

- FP divide, not pipelined: 25 EXE cycles → latency = 24; initiation interval = 25

- Structural hazards can occur when functional unit not fully pipelined (initiation interval > 1) → need to add interlocking

- RAW hazards become longer

- Possibly more than one register write per cycle → either add ports to register file or treat conflict as a hazard and stall

- Possible hazards between integer and FP instructions → use separate register files

for (i=1000; i>0; i--) x[i] = x[i] + s

- Straightforward code and schedule:

- Assume F2 contains the value of s

```

Load latency equals 1

Cycle

- FP ALU latency 3 to another FP ALU and 2 to a store

1

F0,0(R1) ;F0=array element

loop: L.D

2

;add depends on 1d

stall

3

ADD.D F4,F0,F2

;main computation

4

stall

;st depends on add

5

stall

6

S.D F4,0(R1) ; store result

7

DADDUI R1,R1,-8

;decrement index

8

stall

; bne depends on add

9

R1,R2,loop ;next iteration

BNE

10

stall

;branch delay slot

```

Cycle

- Execution time of straightforward code: 10 cycles/element

- Smart compiler (or human ③) schedule:

| loop: | T. D  | F0,0(R1)     | ;F0=array element  | 1 |

|-------|-------|--------------|--------------------|---|

| 1000. |       | R1,R1,-8     | ;decrement index   | 2 |

|       |       | F4,F0,F2     | ;main computation  | 3 |

|       | stall | , ,          | ;st depends on add | 4 |

|       | BNE   | R1, R2, loop | ;next iteration    | 5 |

|       | S.D   | F4,8(R1)     | ;store result      | 6 |

- Immediate offset of store was changed after reordering

- Execution time of scheduled code:

6 cycles/element  $\rightarrow$  Speedup=1.7

Of the 6 cycles, 3 are for actual computation (I.d, add.d, s.d),

2 are loop overhead (addi, bne), and 1 is a stall

Next topic:

handling control hazards through branch prediction

Inf3 Computer Architecture - 2015-2016

- Compiler determines whether branch is likely to be taken or likely to be not taken.

- How?

When is a branch likely to be taken?

When is a branch likely to be NOT taken?

When is a branch likely to be NOT taken?

When is a branch likely to be NOT taken?

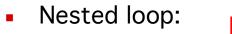

for (i=0;i<1000;i++)

{

x = a[i];

if (x==-1)

{

break;

process(x,i);

}

- Compiler determines whether branch is likely to be taken or likely to be not taken.

- Decision is based on analysis or profile information

- 90% of backward-going branches are taken

- 50% of forward-going branches are not taken

- BTFN: "backwards taken, forwards not-taken"

- Used in ARC 600 and ARM 11

- Decision is encoded in the branch instructions themselves

- Uses 1 bit: 0 => not likely to branch, 1=> likely to branch

- Prediction may be wrong!

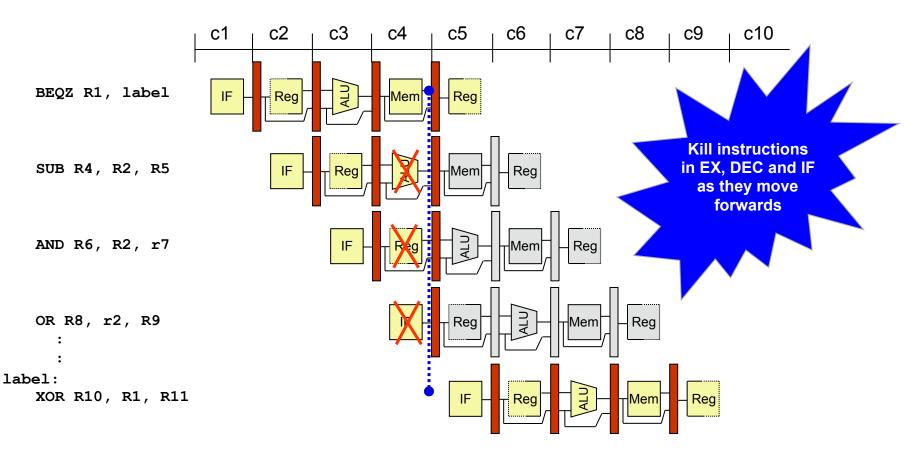

- Must kill instructions in the pipeline when a bad decision is made

- Speculatively issued instructions must not change processor state

#### **Recall: Control Hazards**

- When a branch is executed, PC is not affected until the branch instruction reaches the MEM stage.

- By this time 3 instructions have been fetched from the fall-through path.

- Monitor branch behavior and learn

- Key assumption: past behavior indicative of future behavior

- Predict the present (current branch) using learned history

- Identify individual branches by their PC or dynamic branch history

- Predict:

- Outcome: taken or not taken

- Target: address of instruction to branch to

- Check actual outcome and update the history

- Squash incorrectly fetched instructions

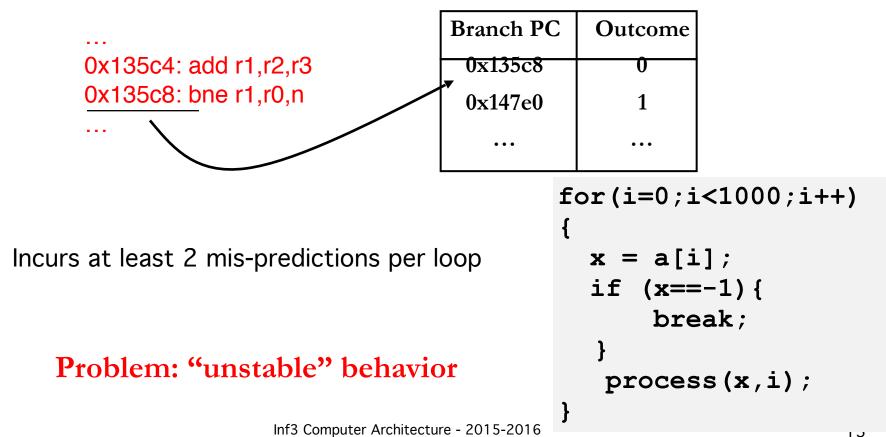

Simplest dynamic predictor: 1-bit Prediction

- 1 bit indicating Taken (1) or Not Taken (0)

- Branch prediction buffers:

- Match branch PC during IF or ID stages

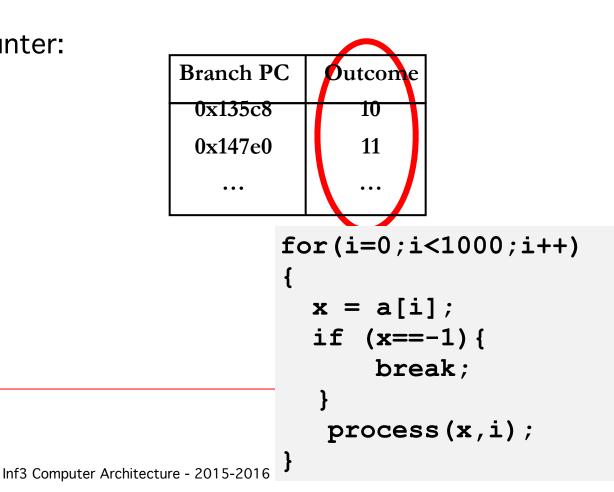

- Idea: add hysteresis

- Prevent spurious events from affecting the most likely branch outcome

- 2-bit saturating counter:

- 00: do not take

- 01: do not take

- 10: take

- 11: take

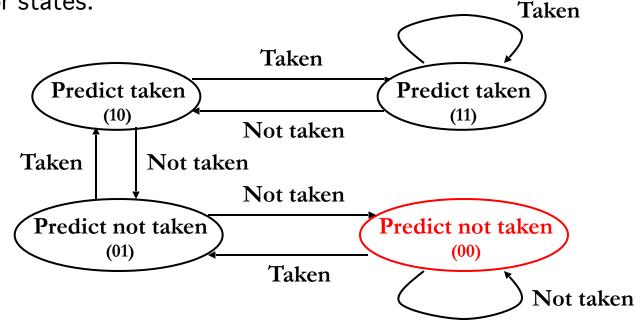

Predictor states:

- Learns biased branches

- N-bit predictor:

- Increment on Taken outcome and decrement on Not Taken outcome

- If counter> $(2^{n}-1)/2$  then take, otherwise do not take

- Takes longer to learn, but sticks longer to the prediction

- 1<sup>st</sup> outer loop execution:

- 00  $\rightarrow$  predict not taken; actually taken  $\rightarrow$  update to 01 (misprediction)

- 01  $\rightarrow$  predict not taken; actually taken  $\rightarrow$  update to 10 (misprediction)

- 10  $\rightarrow$  predict taken; actually taken  $\rightarrow$  update to 11

- 11  $\rightarrow$  predict taken; actually taken

- ...

- $11 \rightarrow$  predict taken; actually not taken  $\rightarrow$  update to 10 (misprediction)

- 2<sup>nd</sup> outer loop execution onwards:

- 10  $\rightarrow$  predict taken; actually taken  $\rightarrow$  update to 11

- $11 \rightarrow$  predict taken; actually taken

- ...

- 11  $\rightarrow$  predict taken; actually not taken  $\rightarrow$  update to 10 (misprediction)

- In practice misprediction rates for 2-bit predictors with 4096 entries in the buffer range from 1% to 18% (higher for integer applications than for fp applications)

- Bottom-line: 2-bit branch predictors work very well for loop-intensive applications

- n-bit predictors (n>2) are not much better

- Larger buffer sizes do not perform much better

- 1- and 2-bit predictors exploit most recent history of the current branch

- Realization: branches are correlated!

If both branches are taken, the last branch definitely <u>not taken</u>

```

char s1 = "Bob"

if (s1 != NULL)

reverse str(s1);

reverse str(char

if (s1 == NUKL

return;

s1 definitely <u>not</u> Null

in this calling context

```

- 1- and 2-bit predictors exploit most recent history of the current branch

- Realization: branches are correlated!

#### Idea: exploit recent history of other branches in prediction

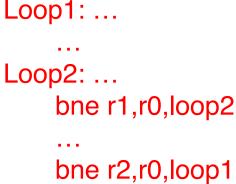

# Two-Level (or Correlating) Predictor

- Prediction depends on the <u>context</u> of the branch

- Context: history (T/NT) of the last N branches

- First level of the predictor

- Implemented as a shift register

- Prediction: 2-bit saturating counters

- Indexed with the "global" history

- Second level of the predictor

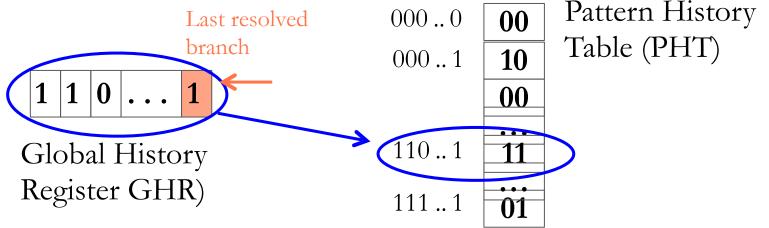

# 2-level predictor improves accuracy by >4%

Inf3 Computer Architecture - 2015-2016

Does 4% accuracy improvement matter?

- Assume branches resolve in stage 10

- Reasonable for a modern high-frequency processor

- 20% of instructions are branches

- Correctly-predicted branches have a 0-cycle penalty (CPI=1)

- 2-bit predictor: 92% accuracy

- 2-level predictor: 96% accuracy

2-bit predictor:

CPI = 0.8 + 0.2 \* (10\*0.08 + 1\*0.92) = 1.114

<u>2-level predictor</u>

CPI = 0.8 + 0.2 \* (10\*0.04 + 1\*0.96) = 1.072

Speedup(2-level over 2-bit): 4%

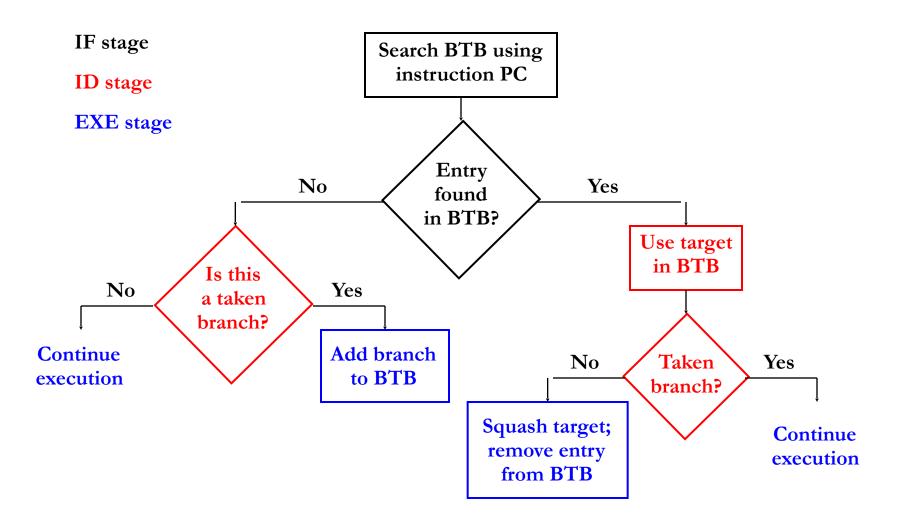

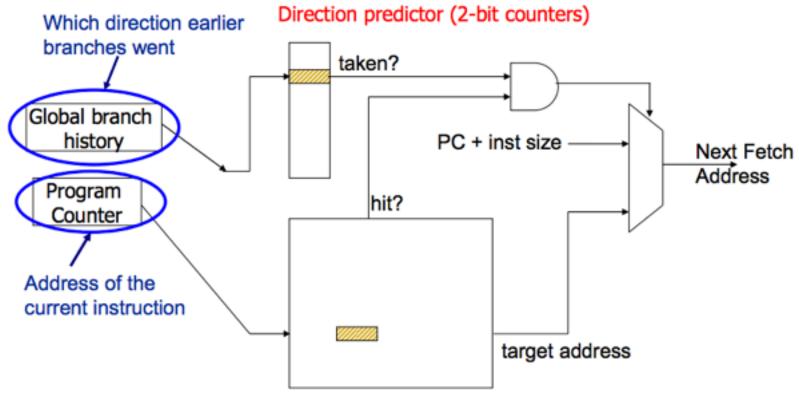

### Branch Target Buffers (BTB)

- Branch predictors tell whether the branch will be taken or not, but they say nothing about the target of the branch

- To resolve a branch early we need to know both the outcome and the target

- Solution: store the likely target of the branch in a table (cache) indexed by the whole of the branch PC  $\rightarrow$  BTB

- Usually BTB is accessed in the IF stage and the branch predictor is accessed soon after that.

- (Aside: In the practical assignment, you will assume a perfect BTB, and a branch predictor that predicts in the fetch stage. Also, branches are resolved in the execute state.)

Cache of Target Addresses (BTB: Branch Target Buffer)

Source: Onur Mutlu, CMU

# Branch Prediction with only BTB